TL494 продолжение.

Автор:jab

Наконец то разродился на очередную поделку и статью. Роды были долгими и мучительными. Ещё раз убеждаюсь, что очень сложно изложить материал по сравнению со сборкой самого устройства. Ну да ладно! Это было предисловие, а суть данного повествования ещё раз прожевать материал об повышающих преобразователях. Для лучшего осмысления поделки изложу немного теории. Поделка работает по принципу «push-pull» или на нашем языке «тяни-толкай». Тяни-толкай это двухтактная схема.

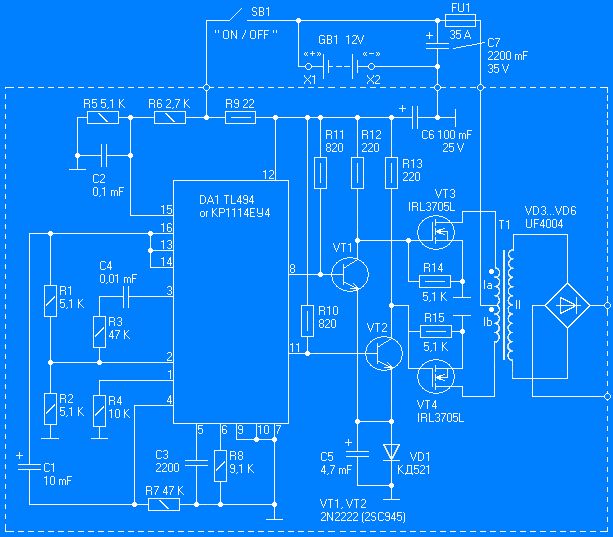

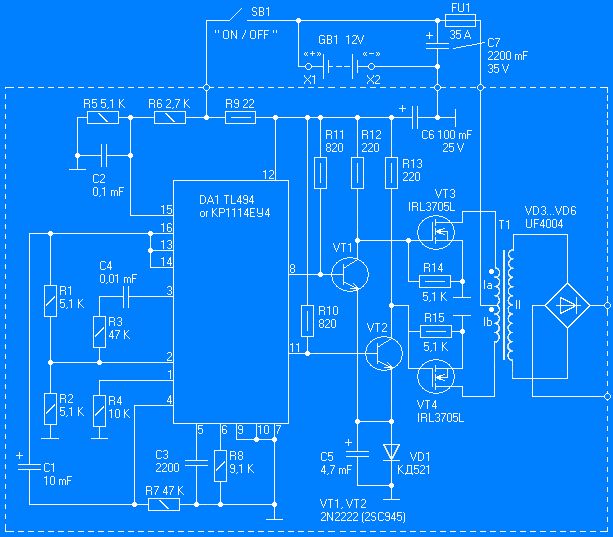

Напомню схему:

Преобразователь состоит из схемы управления ШИМ, каскада форсированного закрывания ключевых транзисторов (VT1 и VT2), двух мощных ключей (VT3, VT4), трансформатора Т1 и выпрямителя на быстрых диодах.

В качестве схемы управления используется микросхема типа TL494CN, выпускаемая фирмой TEXAS INSTRUMENT (США). Она выпускается рядом зарубежных фирм под разными наименованиями. Например, фирма SHARP (Япония) выпускает микросхему IR3M02, фирма FAIRCHILD (США) - иА494, фирма SAMSUNG (Корея) - КА7500, фирма FUJITSU (Япония) - МВ3759 и т.д. Все эти микросхемы являются полными аналогами отечественной микросхемы КР1114ЕУ4.

TL594 - аналог TL494 c улучшенной точностью усилителей ошибки и компаратора.

TL598 - аналог TL594 c двухтактным (pnp-npn) повторителем на выходе.

Плюсы:

Развитые цепи управления, два дифференциальный усилителя (могут выполнять и логические функции)

Минусы:

Однофазные выходы требуют дополнительной обвески (по сравнению с UC3825).

Недоступно токовое управление, относительно медленная петля обратной связи. Синхронное включение двух и более ИС не так удобно, как в UC3825.

Рассмотрим подробно устройство и работу этой управляющей микросхемы. Она специально разработана для управления силовой частью ИБП и содержит в своем составе:

- генератор пилообразного напряжения DA6; частота ГПН определяется номиналами резистора и конденсатора, подключенных к 5-му и 6-му выводам, и в рассматриваемом классе БП выбирается равной примерно 60 кГц;

- источник опорного стабилизированного напряжения DA5 (Uref=+5B) с внешним выходом (вывод 14);

- компаратор "мертвой зоны" DA1;

- компаратор ШИМ DA2;

- усилитель ошибки по напряжению DA3;

- усилитель ошибки по сигналу ограничения тока DA4;

- два выходных транзистора VT1 и VT2 с открытыми коллекторами и эмиттерами;

- динамический двухтактный D-триггер в режиме деления частоты на 2 - DD2;

- вспомогательные логические элементы DD1 (2-ИЛИ), DD3 (2-Й), DD4 (2-Й), DD5 (2-ИЛИ-НЕ), DD6 (2-ИЛИ-НЕ), DD7 (НЕ);

- источник постоянного напряжения с номиналом 0.1B DA7;

- источник постоянного тока с номиналом 0,7мА DA8.

- генератор пилообразного напряжения DA6; частота ГПН определяется номиналами резистора и конденсатора, подключенных к 5-му и 6-му выводам, и в рассматриваемом классе БП выбирается равной примерно 60 кГц;

- источник опорного стабилизированного напряжения DA5 (Uref=+5B) с внешним выходом (вывод 14);

- компаратор "мертвой зоны" DA1;

- компаратор ШИМ DA2;

- усилитель ошибки по напряжению DA3;

- усилитель ошибки по сигналу ограничения тока DA4;

- два выходных транзистора VT1 и VT2 с открытыми коллекторами и эмиттерами;

- динамический двухтактный D-триггер в режиме деления частоты на 2 - DD2;

- вспомогательные логические элементы DD1 (2-ИЛИ), DD3 (2-Й), DD4 (2-Й), DD5 (2-ИЛИ-НЕ), DD6 (2-ИЛИ-НЕ), DD7 (НЕ);

- источник постоянного напряжения с номиналом 0.1B DA7;

- источник постоянного тока с номиналом 0,7мА DA8.

Схема управления будет запускаться, т.е. на 8 и 11 выводах появятся последовательности импульсов в том случае, если на вывод 12 подать любое питающее напряжение, уровень которого находится в диапазоне от +7 до +40 В.

Всю совокупность функциональных узлов, входящих в состав ИМС TL494, можно условно разбить на цифровую и аналоговую часть (цифровой и аналоговый тракты прохождения сигналов).

К аналоговой части относятся усилители ошибок DA3, DA4, компараторы DA1, DA2, генератор пилообразного напряжения DA6, а также вспомогательные источники DA5, DA7, DA8. Все остальные элементы, в том числе и выходные транзисторы, образуют цифровую часть (цифровой тракт).

Временные диаграммы, поясняющие работу микросхемы:

Цифровой тракт.

Из временных диаграмм видно, что моменты появления выходных управляющих импульсов микросхемы, а также их длительность (диаграммы 12 и 13) определяются состоянием выхода логического элемента DD1 (диаграмма 5). Остальная "логика" выполняет лишь вспомогательную функцию разделения выходных импульсов DD1 на два канала. При этом длительность выходных импульсов микросхемы определяется длительностью открытого состояния ее выходных транзисторов VT1, VT2. Так как оба эти транзистора имеют открытые коллекторы и эмиттеры, то возможно двоякое их подключение.

При включении по схеме с общим эмиттером выходные импульсы снимаются с внешних коллекторных нагрузок транзисторов (с выводов 8 и 11 микросхемы), а сами импульсы направлены выбросами вниз от положительного уровня (передние фронты импульсов отрицательны). Эмиттеры транзисторов (выводы 9 и 10 микросхемы) в этом случае, как правило, заземляются. При включении по схеме с общим коллектором внешние нагрузки подключаются к эмиттерам транзисторов и выходные импульсы, направленные в этом случае выбросами вверх (передние фронты импульсов положительны), снимаются с эмиттеров транзисторов VT1, VT2. Коллекторы этих транзисторов подключаются к шине питания управляющей микросхемы (Upom).

Выходные импульсы остальных функциональных узлов, входящих в состав цифровой части микросхемы TL494, направлены выбросами вверх, независимо от схемы включения микросхемы.

Триггер DD2 является двухтактным динамическим D-триггером. Принцип его работы заключается в следующем. По переднему (положительному) фронту выходного импульса элемента DD1 состояние входа D триггера DD2 записывается во внутренний регистр. Физически это означает, что переключается первый из двух триггеров, входящих в состав DD2. Когда импульс на выходе элемента DD1 заканчивается, то по заднему (отрицательному) фронту этого импульса переключается второй триггер в составе DD2, и состояние выходов DD2 меняется (на выходе Q появляется информация, считанная со входа D). Это исключает возможность появления отпирающего импульса на базе каждого из транзисторов VT1, VT2 дважды в течение одного периода.

Действительно, пока уровень импульса на входе С триггера DD2 не изменился, состояние его выходов не изменится. Поэтому импульс передается на выход микросхемы по одному из каналов, например верхнему (DD3, DD5, VT1). Когда импульс на входе С заканчивается, триггер DD2 переключается, запирает верхний и отпирает нижний канал (DD4, DD6, VT2). Поэтому следующий импульс, поступающий на вход С и входы DD5, DD6 будет передаваться на выход микросхемы по нижнему каналу. Таким образом каждый из выходных импульсов элемента DD1 своим отрицательным фронтом переключает триггер DD2 и этим меняет канал прохождения следующего импульса. Поэтому в справочном материале на управляющую микросхему указывается, что архитектура микросхемы обеспечивает подавление двойного импульса, т.е. исключает появление двух отпирающих импульсов на базе одного и того же транзистора за период.

Более подробное описание одного периода работы цифрового тракта микросхемы.

Появление отпирающего импульса на базе выходного транзистора верхнего (VT1) либо нижнего (VT2) канала определяется логикой работы элементов DD5, DD6 ("2ИЛИ-НЕ") и состоянием элементов DD3, DD4 ("2-Й"), которое, в свою очередь, определяется состоянием триггера DD2.

Логика работы элемента 2-ИЛИ-НЕ, как известно, заключается в том, что на выходе такого элемента появляется напряжение высокого уровня (логическая 1) в том лишь единственном случае, если на обоих его входах присутствуют низкие уровни напряжений (логические 0). При остальных возможных комбинациях входных сигналов на выходе элемента 2 ИЛИ-НЕ присутствует низкий уровень напряжения (логический 0). Поэтому если на выходе Q триггера DD2 присутствует логическая 1 (момент t1 диаграммы 5), а на выходе /Q - логический 0, то на обоих входах элемента DD3 (2И) окажутся логические 1 и, следовательно, логическая 1 появится на выходе DD3, а значит и на одном из входов элемента DD5 (2ИЛИ-НЕ) верхнего канала. Следовательно, независимо от уровня сигнала, поступающего на второй вход этого элемента с выхода элемента DD1, состоянием выхода DD5 будет логический О, и транзистор VT1 останется в закрытом состоянии. Состоянием же выхода элемента DD4 будет логический 0, т.к. логический 0 присутствует на одном из входов DD4, поступая туда с выхода /Q триггера DD2. Логический 0 с выхода элемента DD4 поступает на один из входов элемента DD6 и обеспечивает возможность прохождения импульса через нижний канал.

Этот импульс положительной полярности (логическая 1) появится на выходе DD6, а значит и на базе VT2 на время паузы между выходными импульсами элемента DD1 (т.е. на время, когда на выходе DD1 присутствует логический 0 - интервал t1-t2 диаграмма 5). Поэтому транзистор VT2 открывается и на его коллекторе появляется импульс выбросом вниз от положительного уровня (в случае включения по схеме с общим эмиттером).

Начало следующего выходного импульса элемента DD1 (момент t2 диаграммы 5) не изменит состояния элементов цифрового тракта микросхемы, за исключением элемента DD6, на выходе которого появится логический 0, и поэтому транзистор VT2 закроется. Завершение выходного импульса DD1 (момент t3) обусловит изменение состояния выходов триггера DD2 на противоположное (логический 0 - на выходе Q, логическая 1 - на выходе /Q). Поэтому поменяется состояние выходов элементов DD3, DD4 (на выходе DD3 - логический 0, на выходе DD4 - логическая 1). Начавшаяся в момент t3 пауза на выходе элемента DD1 обусловит возможность открывания транзистора VT1 верхнего канала. Логический 0 на выходе элемента DD3 "подтвердит" эту возможность, превращая ее в реальное появление отпирающего импульса на базе транзистора VT1. Этот импульс длится до момента t4, после чего VT1 закрывается, и процессы повторяются.

Таким образом основная идея работы цифрового тракта микросхемы заключается в том, что длительность выходного импульса на выводах 8 и 11 (либо на выводах 9 и 10) определяется длительностью паузы между выходными импульсами элемента DD1. Элементы DD3, DD4 определяют канал прохождения импульса по сигналу низкого уровня, появление которого чередуется на выходах Q и /Q триггера DD2, управляемого тем же элементом DD1. Элементы DD5, DD6 представляют собой схемы совпадения по низкому уровню.

Для полноты описания функциональных возможностей микросхемы следует отметить еще одну важную ее особенность. Как видно из функциональной схемы рисунке входы элементов DD3, DD4 объединены и выведены на вывод 13 микросхемы. Поэтому если на вывод 13 подана логическая 1, то элементы DD3, DD4 будут работать как повторители информации с выходов Q и /Q триггера DD2. При этом элементы DD5, DD6 и транзисторы VT1, VT2 будут переключаться со сдвигом по фазе на половину периода, обеспечивая работу силовой части ИБП, построенной по двухтактной полумостовой схеме. Если на вывод 13 будет подан логический 0, то элементы DD3, DD4 будут заблокированы, т.е. состояние выходов этих элементов не будет изменяться (постоянный логический 0). Поэтому выходные импульсы элемента DD1 будут воздействовать на элементы DD5, DD6 одинаково. Элементы DD5, DD6, а значит и выходные транзисторы VT1, VT2, будут переключаться без сдвига по фазе (одновременно). Такой режим работы управляющей микросхемы используется в случае, если силовая часть ИБП выполнена по однотактной схеме. Коллекторы и эмиттеры обоих выходных транзисторов микросхемы в этом случае объединяются с целью умощнения.

В качестве "жесткой" логической единицы в двухтактных схемах используется выходное напряжение внутреннего источника микросхемы Uref (вывод 13 микросхемы объединяется с выводом 14). Теперь рассмотрим работу аналогового тракта микросхемы.

Состояние выхода DD1 определяется выходным сигналом компаратора ШИМ DA2 (диаграмма 4), поступающим на один из входов DD1. Выходной сигнал компаратора DA1 (диаграмма 2), поступающий на второй вход DD1, не влияет в нормальном режиме работы на состояние выхода DD1, которое определяется более широкими выходными импульсами ШИМ - компаратора DA2.

Кроме того, из диаграмм видно, что при изменениях уровня напряжения на неинвентирующем входе ШИМ компаратора (диаграмма 3) ширина выходных импульсов микросхемы (диаграммы 12, 13) будет пропорционально изменяться. В нормальном режиме работы уровень напряжения на неинвентирующем входе компаратора ШИМ DA2 определяется только выходным напряжением усилителя ошибки DA3 (т.к. оно превышает выходное напряжение усилителя DA4), которое зависит от уровня сигнала обратной связи на его неинвентирующем входе (вывод 1 микросхемы). Поэтому при подаче сигнала обратной связи на вывод 1 микросхемы ширина выходных управляющих импульсов будет изменяться пропорционально изменению уровня этого сигнала обратной связи, который, в свою очередь, изменяется пропорционально изменениям уровня выходного напряжения ИБП, т.к. обратная связь заводится именно оттуда.

Промежутки времени между выходными импульсами на выводах 8 и 11 микросхемы, когда оба выходных транзистора VT1 и VT2 ее закрыты, называются "мертвыми зонами". Компаратор DA1 называется компаратором "мертвой зоны", т.к. он определяет минимально возможную ее длительность.

Из временных диаграмм следует, что если ширина выходных импульсов ШИМ-компаратора DA2 будет в силу каких-либо причин уменьшаться, то начиная с некоторой ширины этих импульсов выходные импульсы компаратора DA1 станут шире выходных импульсов ШИМ-компаратора DA2 и начнут определять состояние выхода логического элемента DD1, а значит и. ширину выходных импульсов микросхемы. Другими словами, компаратор DA1 ограничивает ширину выходных импульсов микросхемы на некотором максимальном уровне. Уровень ограничения определяется потенциалом на неинвентирующем входе компаратора DA1 (вывод 4 микросхемы) в установившемся режиме. Однако с другой стороны, потенциал на выводе 4 будет определять диапазон широтной регулировки выходных импульсов микросхемы. При увеличении потенциала на выводе 4 этот диапазон сужается. Самый широкий диапазон регулировки получается тогда, когда потенциал на выводе 4 равен 0.

Однако в этом случае появляется опасность, связанная с тем, что ширина "мертвой зоны" может стать равной 0 (например, в случае значительного возрастания потребляемого от ИБП тока). Это означает, что управляющие импульсы на выводах 8 и 11 микросхемы будут следовать непосредственно друг за другом. Поэтому может возникнуть ситуация, известная под названием "пробой по стойке". Она объясняется инерционностью силовых транзисторов инвертора, которые не могут открываться и закрываться мгновенно. Поэтому, если одновременно на базу открытого до этого транзистора подать запирающий сигнал, а на базу закрытого транзистора - отпирающий (т.е. с нулевой "мертвой зоной"), то получится ситуация, когда один транзистор еще не закрылся, а другой уже открыт.

Тогда и возникает пробой по транзисторной стойке полумоста, который заключается в протекании сквозного тока через оба транзистора. Ток этот минует первичную обмотку силового трансформатора и практически ничем не ограничен. Защита по току в этом случае не работает, т.к. ток не протекает через токовый датчик (на схеме не показан), а значит, этот датчик не может выдать сигнал на схему управления. Поэтому сквозной ток достигает очень большой величины за очень короткий промежуток времени.

Подобная ситуация приведёт к перегреву силовых транзисторов и их пробою. Поэтому управляющее напряжение, подаваемое на затворы силовых транзисторов, должно быть сформировано таким образом, чтобы сначала надежно закрывался бы один из этих транзисторов, а уже потом открывался бы другой. Другими словами, между управляющими импульсами, подаваемыми на затворы силовых транзисторов обязательно должен быть временной сдвиг, не равный нулю ("мертвая зона"). Минимальная допустимая длительность "мертвой зоны" определяется инерционностью применяемых в качестве силовых ключей транзисторов. Другая неприятность заключается в том, что конечное время востановления выпрямительных диодов может оказаться значительно больше "мертвой зоны". Это связано с тем, что реальные диоды, в отличии от идеальных, не могут мгновенно закрываться и через них могут протекать токи в обратном направлении, это ведёт к потерям, перегреванию и выходу из строя. Во избежание коммутационных выбросов, во-первых, необходимо введение "мертвой зоны" между закрытием транзистора VT3 и открытием VT4 не менее чем удвоенное время обратного восстановления диода. Во-вторых, если есть возможность, лучше отказаться от обычных диодов и применить диоды Шоттки (Диоды Шоттки как правило на низкое оратное напряжение. Их имеет особый смысл применять в понижающих преобразователях).

Итак, в идеальной схеме сигнал на затворах будет равняться пол периода D=0.5, но в реальной схеме, по описанным выше причинам, мы обязательно добавляем «мертвую зону» и в результате получаем импульс в лучшем случае D=0.45.

Архитектура микросхемы позволяет регулировать величину минимальной длительности "мертвой зоны" с помощью потенциала на выводе 4 микросхемы. Потенциал этот задается с помощью внешнего делителя, подключаемого к шине выходного напряжения внутреннего опорного источника микросхемы Uref.

В некоторых вариантах ИБП такой делитель отсутствует. Это означает, что после завершения процесса плавного пуска (см. ниже) потенциал на выводе 4 микросхемы становится равным 0. В этих случаях минимально возможная длительность "мертвой зоны" все же не станет равной 0, а будет определяться внутренним источником напряжения DA7 (0,1В), который подключен к неинвертирующему входу компаратора DA1 своим положительным полюсом, и к выводу 4 микросхемы - отрицательным. Таким образом, благодаря включению этого источника ширина выходного импульса компаратора DA1, а значит и ширина "мертвой зоны", ни при каких условиях не может стать равной 0, а значит "пробой по стойке" будет принципиально невозможен.

Другими словами, в архитектуру микросхемы заложено ограничение максимальной длительности ее выходного импульса (минимальной длительности "мертвой зоны").

Если имеется делитель, подключенный к выводу 4 микросхемы, то после плавного пуска потенциал этого вывода не равен 0, поэтому ширина выходных импульсов компаратора DA1 определяется не только внутренним источником DA7, но и остаточным (после завершения процесса плавного запуска) потенциалом на выводе 4. Однако при этом, как было сказано выше, сужается динамический диапазон широтной регулировки ШИМ компаратора DA2.

Рассмотрим работу силовых ключей.

При работе на емкостную нагрузку, какой условно является затвор полевого транзистора, выходные транзисторы TL494 включаются эмитерным повторителем. При ограничении среднего тока в 200 мА схема способна достаточно быстро зарядить затвор, но разрядить его выключенным транзистором невозможно. Разряжать затвор с помощью заземленного резистора - также неудовлетворительно медленно. Ведь напряжение на условной емкости затвора спадает по экспоненте, а для закрытия транзистора затвор надо разрядить от 10В до не более 3В. Ток разряда через резистор будет всегда меньше тока заряда через транзистор (да и греться резистор будет неслабо, и красть ток ключа при ходе вверх).

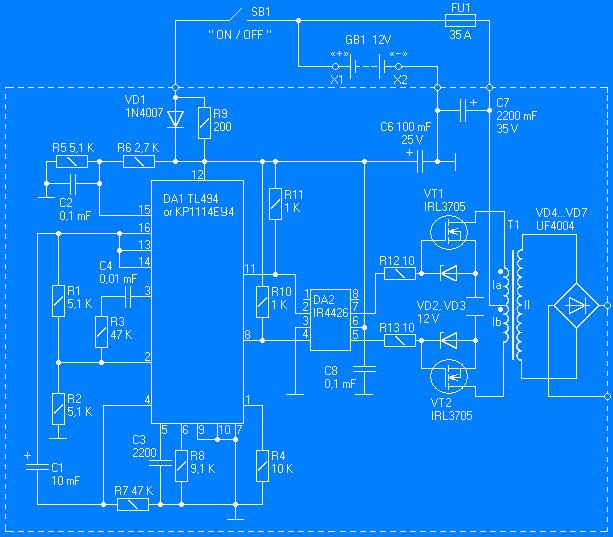

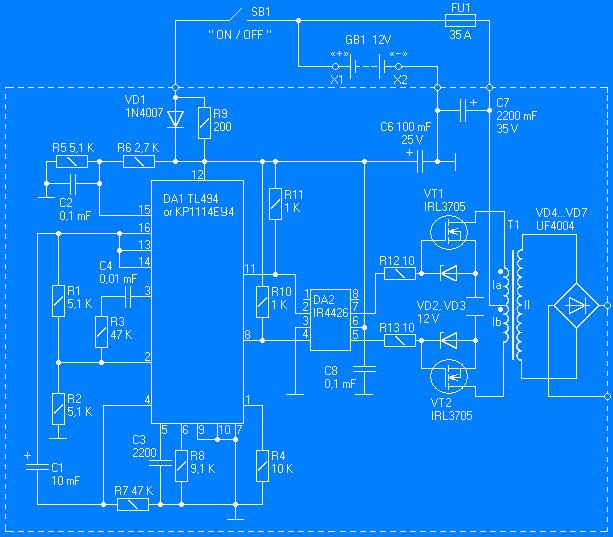

Что бы обойти все эти проблемы в нашем варианте был реализован каскада форсированного закрывания ключевых транзисторов. Почему закрытия? Потому что у нас схема работает в инверсном режиме. К примеру, возьмем один такт. В микросхеме образовался сигнал и открылся один из её ключей (возьмем верхний по схеме) и коммутировал резистор R11 на землю и этим самым обесточил базу VT1 (закрыл его). С этого момента ток начинает течь через резистор R12 и заряжать емкость затвора VT3. Зарядившись до состояния насыщения, транзистор открывается. В момент отключения сигнала в микросхеме у нас VT1 открывается и коммутирует затвор силового на землю и разряжает его до закрытия. То же самое во втором ключе, но в противофазе. Транзистор VT1 разряжает затвор полевика и частично проводит ток с резистора R12. Это дополнительная нагрузка на транзистор VT1 и потеря КПД. Особенно хорошо это проявляется на высоких частотах. Это можно излечить поставив нормальный эмитерный повторитель, но это увеличивает количество деталей и размеры платы. По последней причине я решил поставить специализированный MOSFET драйвер IR4426. Подробно объяснять его структуру не стану. Этот драйвер выпускается широко известной фирмой International Rectifier (IR). Естественно есть аналоги других фирм. Микросхема представляет из себя специализированный инверсный драйвер двух полевых затворов.

Новая схема:

Резисторы R12 и R13 по 10 Ом для ограничения тока драйвера. Стабилитроны VD2 и VD3 маломощные на 12-15 вольт, для защиты затворов от случайных бросков напряжения.

Напряжение на закрытом ключевом транзисторе складывается из напряжения питания и ЭДС первичной полуобмотки, которая в данный момент разомкнута. Поскольку коэффициент трансформации этих обмоток равен 1 (обмотки с одинаковым числом витков), перенапряжение на ключевом транзисторе достигает двойного значения напряжения питания. Поэтому выбирать транзисторы по допустимому напряжению между силовыми электродами следует из данного условия. Необходимо также учитывать, что ток ключевого транзистора складывается из постоянного тока нагрузки, пересчитанного в первичную цепь, и линейно нарастающего тока намагничивания индуктивности первичной обмотки. Ток имеет трапециевидную форму.

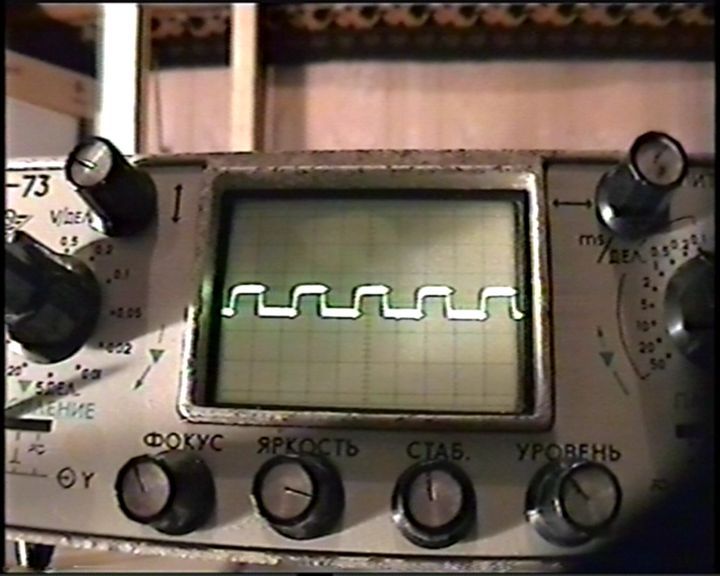

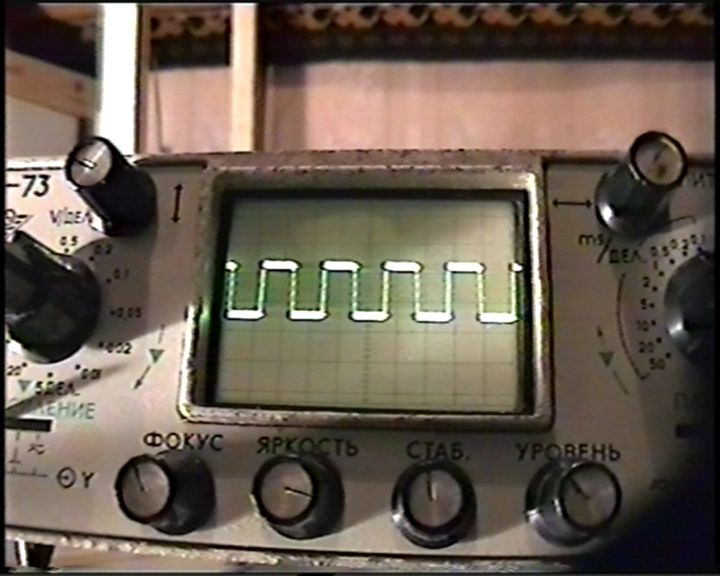

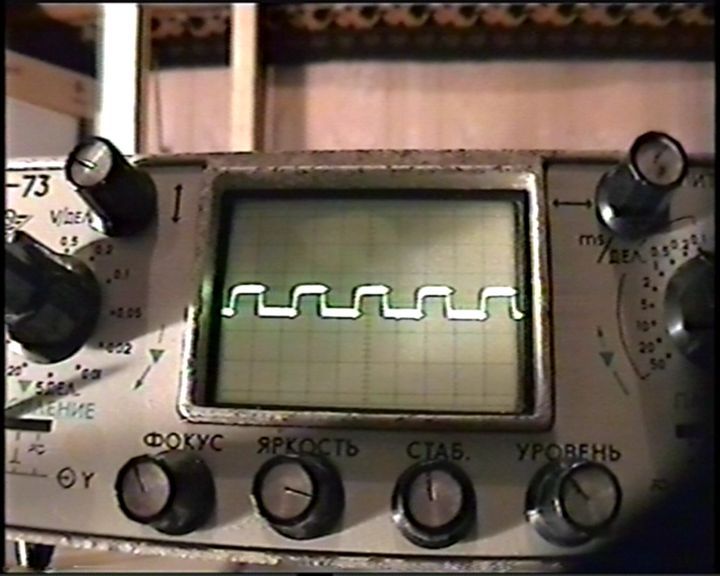

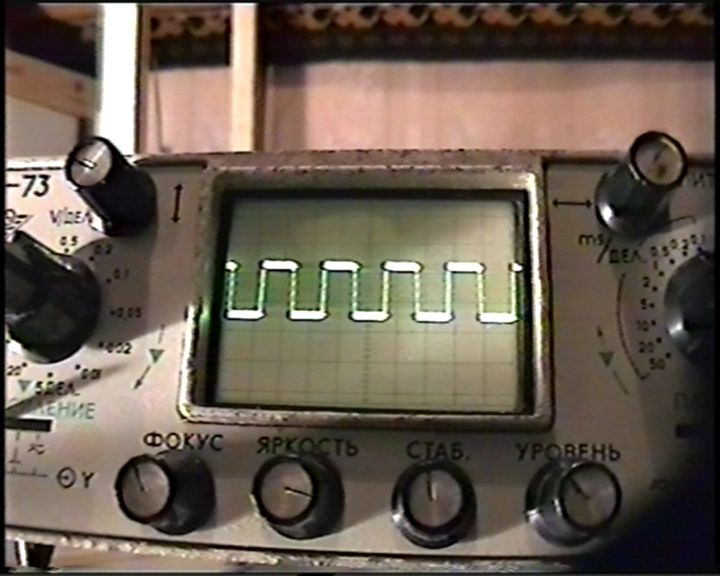

У кого есть осцик, то вы можете всё это увидать собственными глазами. К примеру вот напряжения на участках затвор-сток и исток-сток.

Из второго рисунка мы как раз и видим двойное значение напряжения на истоке силового транзистора.

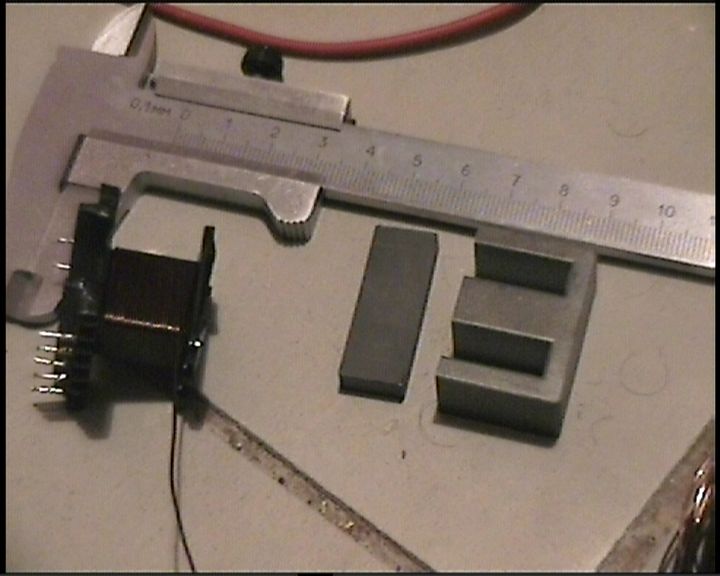

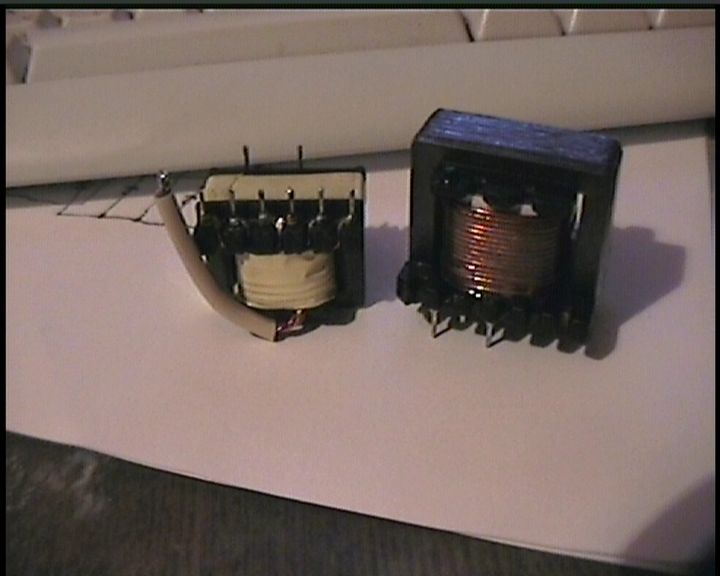

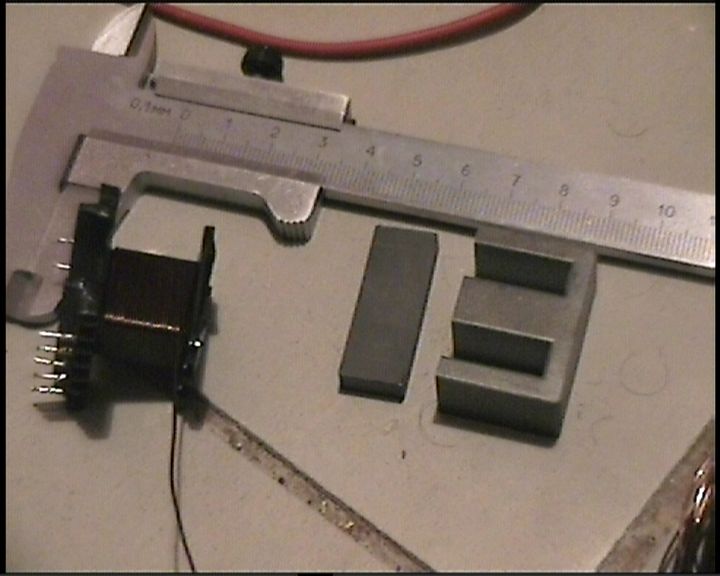

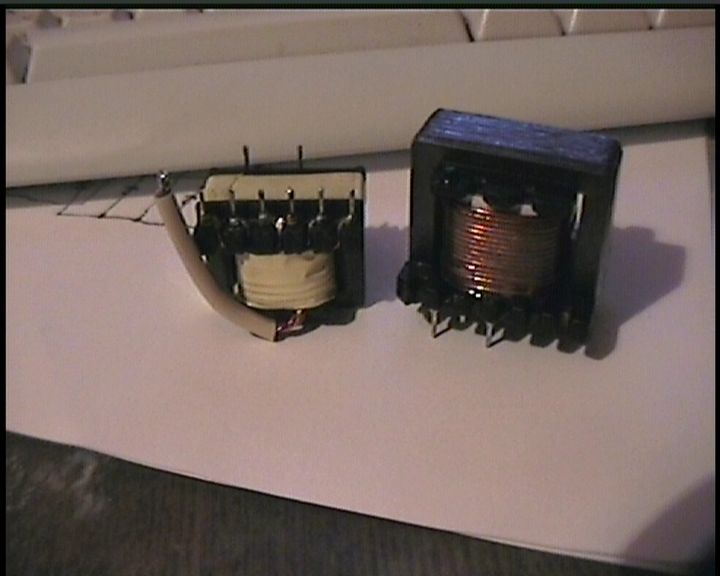

Трансформатор Ш 10x13 образный без зазора. ширина = 10мм толщина = 13мм высота просвета 19мм (рабочая высота катушки 17мм)

первичка = 4 + 4 витка двойным проводом 0.85 (укладывал лентой в 4 жилы)

вторичка = 84 витка проводом 0.6 (четыре слоя по 21 витку, умещается больше витков,

но я оставлял свободное место по краям).

Первой наматывал вторичку 4 слоя с изоляцией между слоями.

Последней укладывал вторичку одним слоем лентой в 4 провода.

При указанных на схеме номиналах конденсатора C3 и сопротивления R8, частота преобразования составит порядка 40 кГц. Входное напряжение 12 вольт, выходное 250 вольт. Для больших значений выходного напряжение следует пересчитать число витков вторичной обмотки исходя из трех вольт на виток. Можно просто умножитель поставить и не парится.

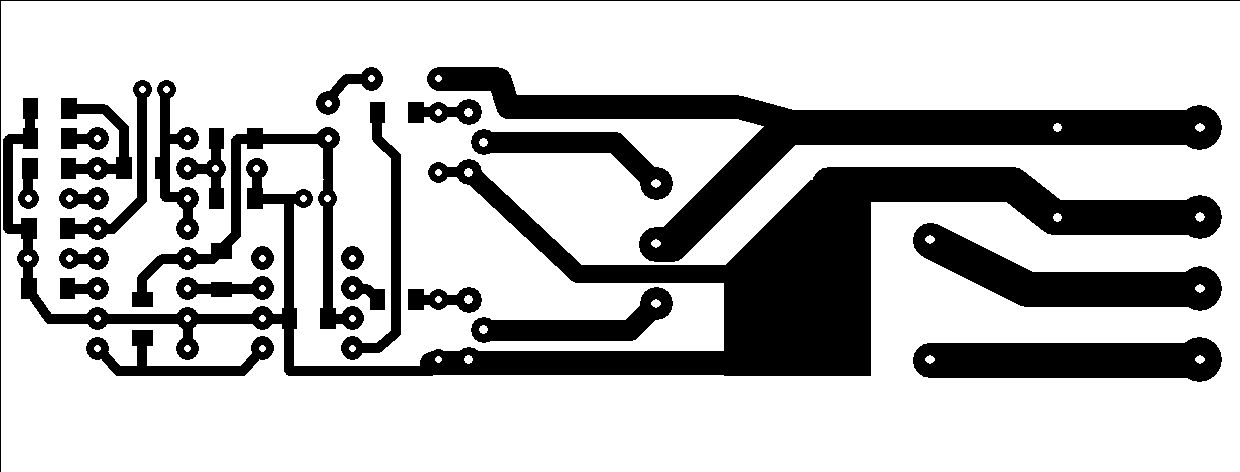

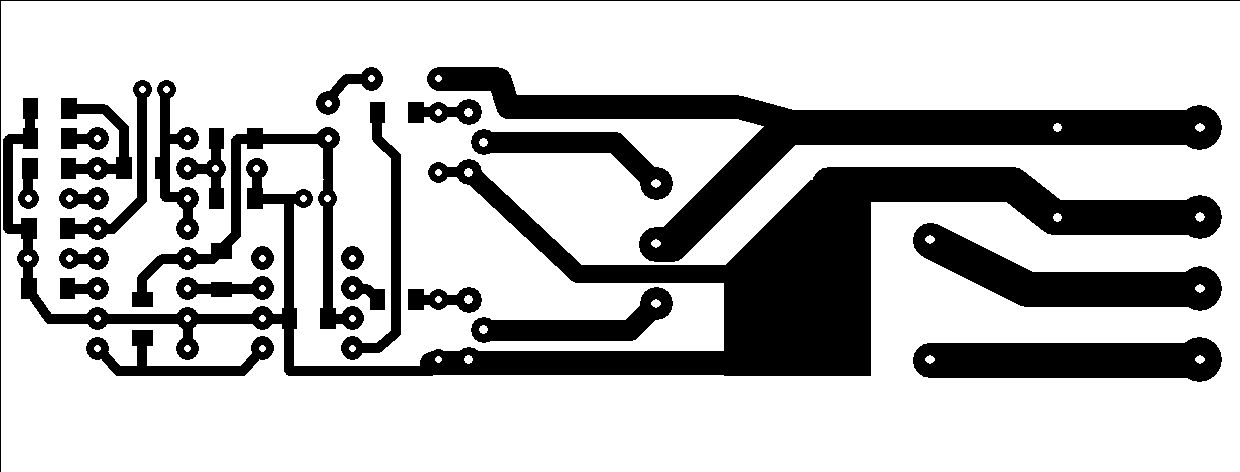

Для сборки устройства вам понадобится лазерный принтер, глянцевая бумага от женского журнала, утюг, фальгированный стеклотекстолит, хлорное железо, дрель со сверлами, радиодетали, терпение и пару бутылок холодного пива с сухариками.

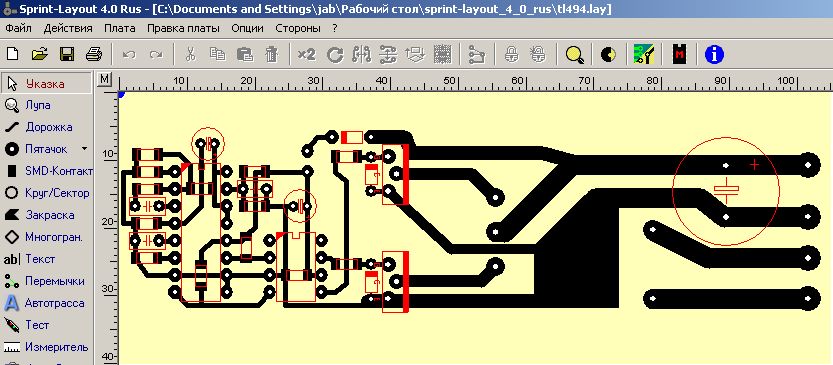

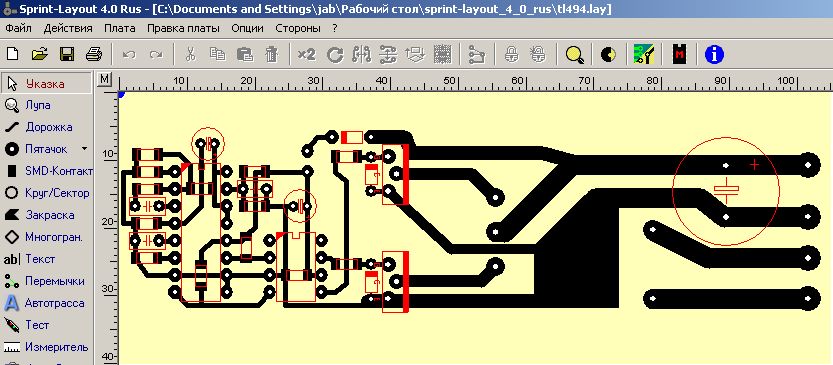

Схему рисовал в четвертом Layout'e. Схему скачать можно тут.

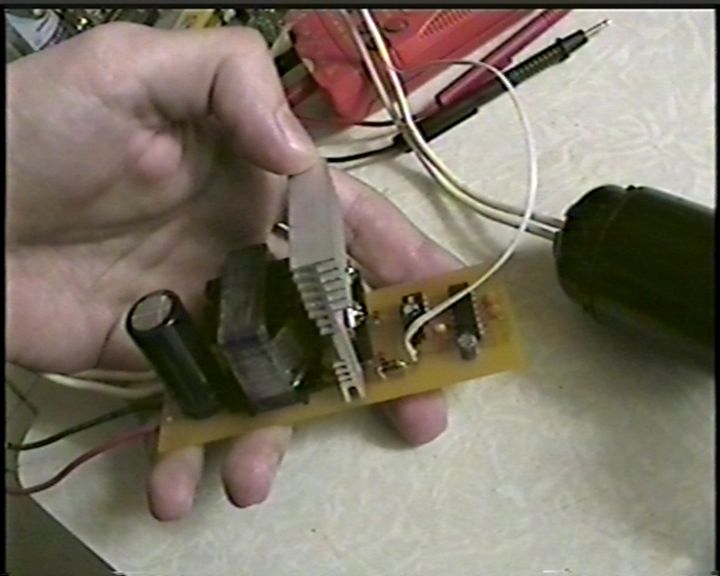

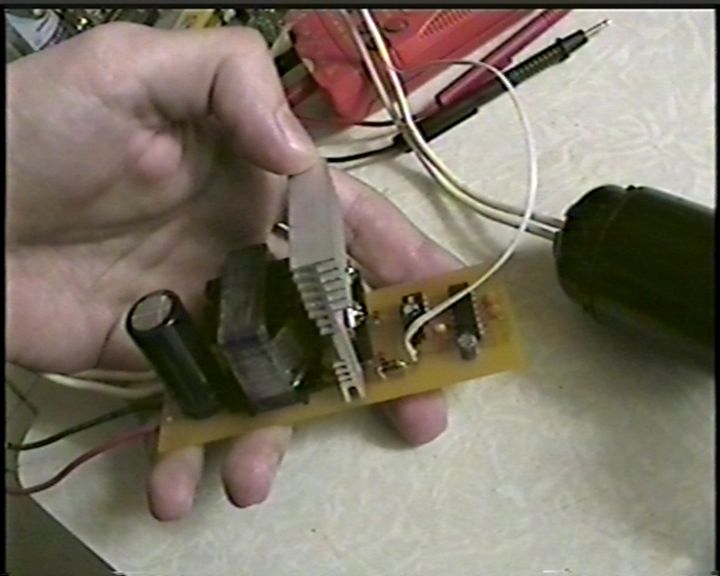

Печатаем на принтере, утюжим, смываем бумагу, вытравливаем, сверлим отверстия, смываем лишний мусор, лудим, напаиваем детали. Правильно собранное устройство не требует дополнительных настроек и работает сразу. Единственное замечание заключается в том, что силовые дорожки на плате необходимо усилить, пропаяв их с дополнительными обрезками медной жилы нужного диаметра. Конденсаторы C7 необходимо использовать с низкой собственной индуктивностью.

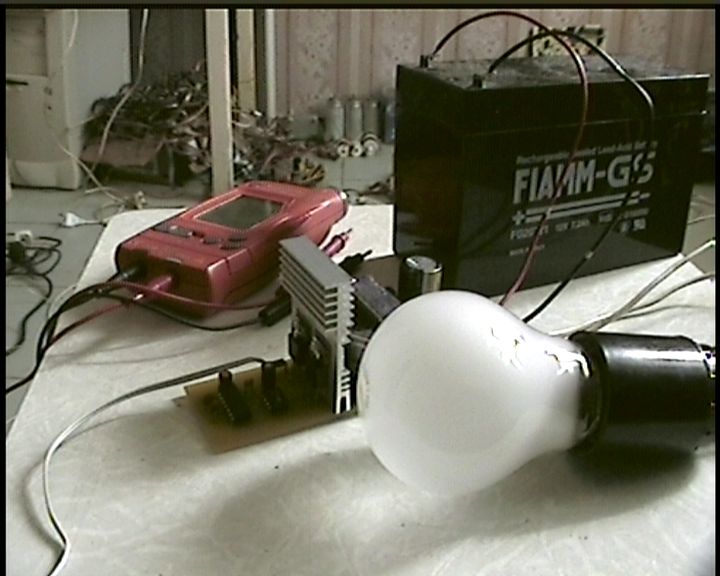

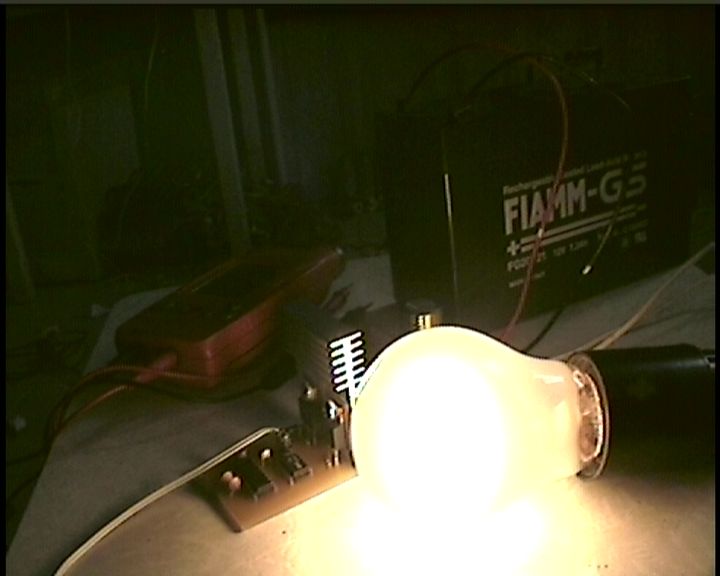

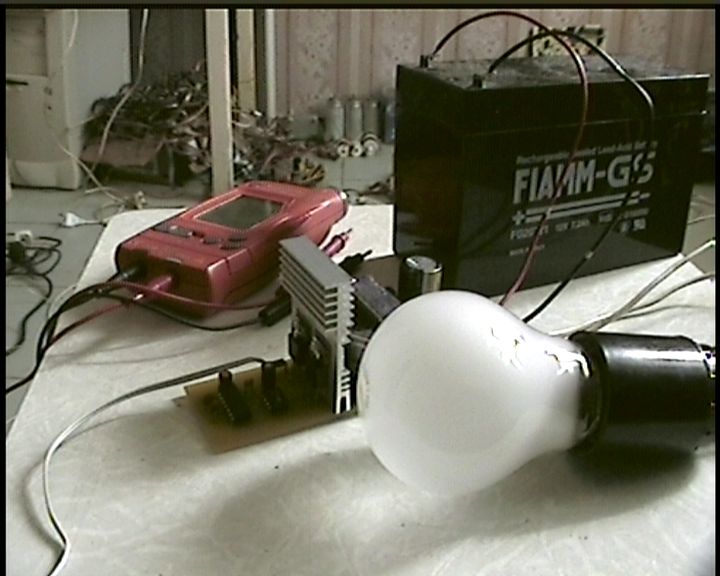

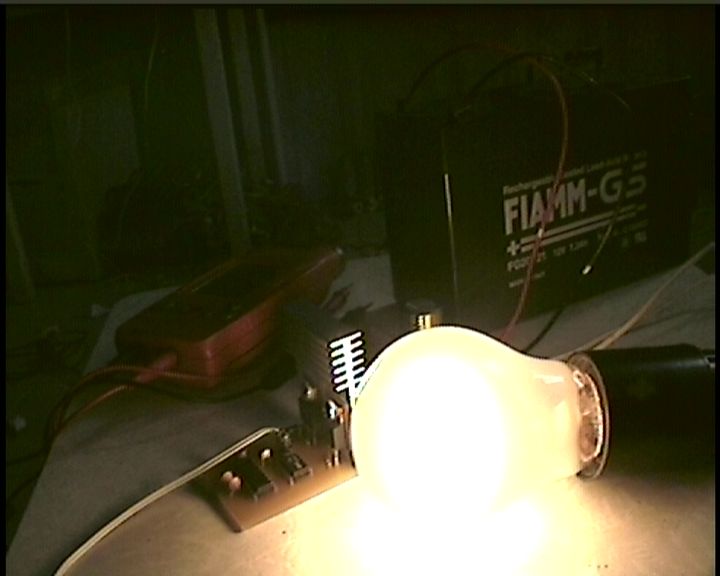

В моем случае всё заработало как нужно. На холостом ходу, без какой либо нагрузки, преобразователь потреблял в районе 150 миллиампер. Номинальная выходная мощность 100 Вт. Максимальная 150Вт с дополнительным охлаждением.

На второй картинке на самом деле не ночь, просто у меня так камера реагирует на яркое свечение (типа автоподстройка яркости). Лампа светит немного ярче обычного.

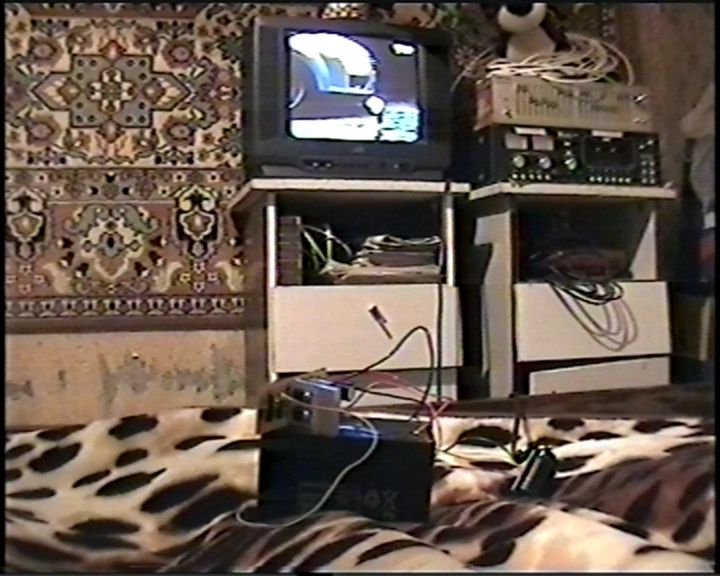

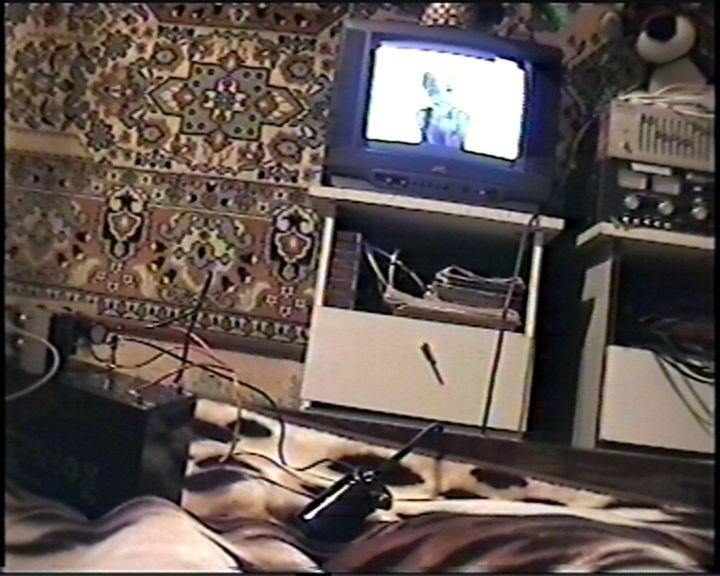

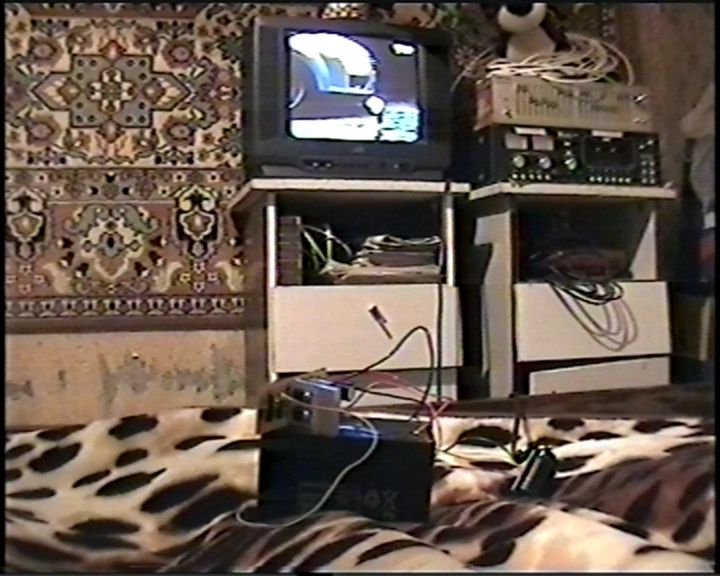

Мощности в полнее хватает, что бы запитать небольшой телевизор.

Оказалось, что телевизор потребляет всего 60Вт, что меньше лампочки.

Недостатком является отсутствие защиты от короткого замыкания по вторичке (ограничение тока силовых ключей), отсутствие контроля выходного напряжения и необходимостью использовать дополнительный драйвер. Для более надежной работы схемы (предохранение переходов от перенапряжений - выбросы в виде иголок), силовые ключи можно обвесить снабберами или супресорами. Про эти и другие вещи в следующей части. В прочем вы можете попробовать собрать эту хрень ради спортивного интереса. Отдельное большое спасибо товарищу Jaxon'у за полезные уточнения материала.

К списку статей |